For purposes of illustration, 10 replications of each of the four designs were run, using independent sampling (i.e., different random numbers for all runs). The results are presented in Table 12.6, together with sample means  $(\overline{Y_i})$ , sample standard deviations  $(S_i)$ , and sample variances  $(S_i^2)$ , plus the observed difference of sample means  $(\overline{Y_i} - \overline{Y_i})$  and the standard error (s.e.) of the observed difference. It is observed that all three confidence intervals for  $\theta_1 - \theta_i (i = 2, 3, 4)$  contain zero. Therefore, no strong conclusion is possible from these data and this sample size. By contrast, a sample size of ten was sufficient, when using CRN, to provide strong evidence that design 3 is superior to design 1.

Notice the large increase in standard error of the estimated difference with independent sampling versus with common random numbers. These standard errors are compared in Table 12.7. In addition, a careful examination of Tables 12.5 and 12.6 illustrates the superiority of CRN. In Table 12.5, in all 10 replications, system design 3 has a smaller average response time than does system design 1. By comparing replications 1 and 2 in Table 12.5, it can be seen that a random-number stream that leads to high congestion and large response times in system design 1, as in the first replication, produces results of similar magnitude across all four system designs. Similarly, when system designs I exhibits relatively low congestion and low response times, as in the second replication, all system designs produce relatively low average response times. This similarity of results on each replication is due, of course, to the use of common random numbers across systems. By contrast, for independent sampling, Table 12.6 shows no such similarity across system designs. In only 5 of the 10 replications is the average response time for system design 3 smaller than that for system design 1, although the average difference in response times across all 10 replications is approximately the same magnitude in each case: 5.69 minutes when using CRN, and 5.89 minutes when using independent

**Table 12.6** Analysis of Output Data for the Vehicle-Inspection System that Uses Independent Sampling

|                                          | Average Response Time for System Design |                       |                    |                       |  |  |  |

|------------------------------------------|-----------------------------------------|-----------------------|--------------------|-----------------------|--|--|--|

| Replication,<br>r                        | $I, Y_{r1}$                             | 2,<br>Y <sub>r2</sub> | $\frac{3}{Y_{e3}}$ | 4,<br>Y <sub>r4</sub> |  |  |  |

| 1                                        | 63.72                                   | 59.37                 | 52.00              | 59.03                 |  |  |  |

| 2                                        | 32.24                                   | 50.06                 | 47.04              | 49.97                 |  |  |  |

| 3                                        | 40.28                                   | 60.63                 | 53.21              | 60.18                 |  |  |  |

| 4                                        | 36.94                                   | 46.36                 | 40.88              | 45.44                 |  |  |  |

| 5                                        | 36.29                                   | 68.87                 | 50.85              | 66.65                 |  |  |  |

| 6                                        | 56.94                                   | 66.44                 | 60.42              | 66.03                 |  |  |  |

| 7                                        | 34.10                                   | 27.51                 | 26.70              | 27.45                 |  |  |  |

| 8                                        | 63.36                                   | 47.98                 | 40.12              | 47.50                 |  |  |  |

| . 9                                      | 49.29                                   | 29.92                 | 28.59              | 29.84                 |  |  |  |

| 10                                       | 87.20                                   | 47.14                 | 41.62              | 46.44                 |  |  |  |

| Sample mean $ar{Y}_i$                    | 50.04                                   | 50.43                 | 44.14              | 49.85                 |  |  |  |

| $S_{i}$                                  | 17.70                                   | 13.98                 | 10.76              | 13.64                 |  |  |  |

| $\frac{S_i}{S_i^2}$                      | 313.38                                  | 195.54                | 115.74             | 185.98                |  |  |  |

| $\overline{Y}_{_1} - \overline{Y}_{_i}$  |                                         | -0.39                 | 5.89               | 0.18                  |  |  |  |

| s.e. $(\overline{Y}_1 - \overline{Y}_i)$ |                                         | 7.13                  | 6.55               | 7.07                  |  |  |  |

|                                           | Standard Err    |                         |                        |

|-------------------------------------------|-----------------|-------------------------|------------------------|

| Difference in<br>Sample Means             | CRN<br>Sampling | Independent<br>Sampling | Percentage<br>Increase |

| $\overline{Y}_{1} - \overline{Y}_{2}$     | 0.67            | 7.13                    | 1064%                  |

| $\overline{Y}_1 - \overline{Y}_3$         | 1.69            | 6.55                    | 388%                   |

| $\overline{Y}_{_{1}}-\overline{Y}_{_{2}}$ | 0.74            | 7.07                    | 955%                   |

**Table 12.7** Comparison of Standard Errors Arising from CRN with those from Independent Sampling, for the Vehicle-Inspection Problem

sampling. The greater variability of independent sampling is reflected also in the standard errors of the point estimates:  $\pm 1.69$  minutes for CRN versus  $\pm 6.55$  minutes for independent sampling, an increase of 388%, as seen in Table 12.7. This example illustrates again the advantage of CRN.

As stated previously, CRN does not yield a variance reduction in all simulation models. It is recommended that a pilot study be undertaken and variances estimated to confirm (or possibly deny) the assumption that CRN will reduce the variance (or standard error) of an estimated difference. The reader is referred to the discussion in Section 12.1.3.

Some of the exercises at the end of this chapter provide an opportunity to compare CRN and independent sampling and to compute simultaneous confidence intervals under the Bonferroni approach.

#### 12.2.2 Bonferroni Approach to Selecting the Best

Suppose that there are K system designs, and the ith design has expected performance  $\theta_i$ . At a gross level, we are interested in which system is best, where "best" is defined to be having maximum expected performance. At a more refined level, we could also be interested in how much better the best is relative to each alternative, because secondary criteria that are not reflected in the performance measure  $\theta_i$  (such as ease of installation, cost to maintain, etc.) could tempt us to choose an inferior system if it is not deficient by much.

If system design i is the best, then  $\theta_i - \max_{j \neq i} \theta_j$  is equal to the difference in performance between the best and the second best. If system design i is not the best, then  $\theta_i - \max_{j \neq i} \theta_j$  is equal to the difference between system i and the best. The selection procedure we describe in this section focuses on the parameters  $\theta_i - \max_{i \neq i} \theta_i$  for i = 1, 2, ..., K.

Let  $i^*$  denote the (unknown) index of the best system. As a general rule, the smaller the true difference  $\theta_i$ ,  $-\max_{j\neq i^*}\theta_j$  is, and the more certain we want to be that we find the best system, the more replications are required to achieve our goal. Therefore, instead of demanding that we find  $i^*$ , we can compromise and ask to find  $i^*$  with high probability whenever the difference between system  $i^*$  and the others is at least some practically significant amount. More precisely, we want the probability that we select the best system to be at least  $1-\alpha$  whenever  $\theta_{i^*}-\max_{j\neq i^*}\theta_j \geq \epsilon$ . If there are one or more systems that are within  $\epsilon$  of the best, then we will be satisfied to select either the best or any one of the near best. Both the probability of correct selection,  $1-\alpha$ , and the practically significant difference,  $\epsilon$ , will be under our control.

The following procedure achieves the desired probability of correct selection (Nelson and Matejcik [1995]). And because we are also interested in how much each system differs from the best, it also forms  $100(1-\alpha)\%$  confidence intervals for  $\theta_i$ ,  $-\max_{i\neq i}\theta_j$  for i=1,2,...,K. The procedure is valid for normally distributed data when either CRN or independent sampling is being used.

<sup>&</sup>lt;sup>1</sup>If "best" is defined to be having minimum expected performance, then the procedure in this section is easily modified, as we illustrate in the example.

#### **Two-Stage Bonferroni Procedure**

- 1. Specify the practically significant difference  $\epsilon$ , the probability of correct selection  $1 \alpha$ , and the first-stage sample size  $R_0 \ge 10$ . Let  $t = t_{\alpha/(K-1),R_0-1}$ .

- **2.** Make  $R_0$  replications of system i to obtain  $Y_{1i}, Y_{2i}, ..., Y_{R_0,i}$ , for systems i = 1, 2, ..., K.

- 3. Calculate the first-stage sample means  $\overline{Y}_i$ , i = 1, 2, ..., K. For all  $i \neq j$ , calculate the sample variance of the difference.<sup>2</sup>

$$S_{ij}^{2} = \frac{1}{R_{ii} - 1} \sum_{j=1}^{R_{ii}} (Y_{ij} - Y_{ij} - (\overline{Y}_{i} - \overline{Y}_{j}))^{2}$$

Let  $\hat{S}^2 = \max_{i \neq j} S_{ii}^2$ , the largest sample variance.

4. Calculate the second-stage sample size,

$$R = \max \left\{ R_0, \left[ \frac{t^2 \hat{S}^2}{\epsilon^2} \right] \right\}$$

where [.] means to round up.

- **5.** Make  $R R_0$  additional replications of system i to obtain the output data  $Y_{R_0+1,i}, Y_{R_0+2,i}$ , for i = 1, 2, ..., K.

- **6.** Calculate the overall sample means

$$\overline{\overline{Y}}_i = \frac{1}{R} \sum_{r=1}^R Y_{ri}$$

for i = 1, 2, ..., K.

7. Select the system with largest  $\overline{\overline{Y}}$  as the best.

Also form the confidence intervals

$$\min\{0, \overline{\overline{Y}}_i - \max_{j \neq i} \overline{\overline{Y}}_j - \epsilon\} \leq \theta_i - \max_{j \neq i} \theta_j \leq \max\{0, \overline{\overline{Y}}_i - \max_{j \neq i} \overline{\overline{Y}}_i^T + \epsilon\}$$

for

$$i = 1, 2, ..., K$$

.

The confidence intervals in Step 7 are not like the usual  $\pm$  intervals presented elsewhere in this chapter. Perhaps the most useful interpretation of them is as follows. Let  $\hat{i}$  be the index of the system selected as best. Then, for each of the other systems i, we make one of the declarations:

- If  $\overline{\overline{Y}}_i \overline{\overline{Y}}_i + \epsilon \le 0$ , then declare system *i* to be inferior to the best.

- If  $\overline{Y}_i \overline{Y}_j + \epsilon > 0$ , then declare system *i* to be statistically indistinguishable from the best (and, therefore, system *i* might be the best).

#### **Example 12.4: Continued**

Recall that, in Example 12.4, we considered K = 4 different designs for the vehicle-inspection station. Suppose that we would like 0.95% confidence of selecting the best (smallest expected response time) system design when

Notice that  $S_{ii}^2$  is algebraically equivalent to  $S_{D}^2$ , the sample variance of  $D_r = Y_{ri} - Y_{ri}$ , for  $r = 1, 2, ..., R_{0}$ .

If it is more convenient, a total of R replications can be generated from system i by restarting the entire experiment,

the best differs from the second best by at least two minutes. This is a minimization problem, so we focus on the differences  $\theta_i - \min_{j \neq i} \theta_j$  for i = 1, 2, 3, 4. Then we can apply the Two-Stage Bonferroni Procedure as follows:

- 1.  $\epsilon = 2$  minutes,  $1 \alpha = 0.95$ ,  $R_0 = 10$ , and  $t = t_{0.0167.9} = 2.508$ .

- 2. The data in Table 12.5, which was obtained by using CRN, is employed.

- **3.** From Table 12.5, we get  $S_{12}^2 = S_{D_2}^2 = 4.498$ ,  $S_{13}^2 = S_{D_2}^2 = 28.498$ , and  $S_{14}^2 = S_{D_2}^2 = 5.489$ . By similar calcultions, we obtain  $S_{23}^2 = 11.857$ ,  $S_{24}^2 = 0.119$ , and  $S_{34}^2 = 9.849$ .

- **4.** Since  $\hat{S}^2 = S_{13}^2 = 28.498$  is the largest sample variance,

$$R = \max\left\{10, \left\lceil \frac{(2.508)^2 (28.498)}{2^2} \right\rceil \right\} = \max\left\{10, \left\lceil 44.8 \right\rceil \right\} = 45$$

- 5. Make 45 10 = 35 additional replications of each system.

- **6.** Calculate the overall sample means

$$\overline{\overline{Y}}_{i} = \frac{1}{45} \sum_{r=1}^{45} Y_{rr}$$

for i = 1, 2, 3, 4.

7. Select the system with smallest  $\overline{\overline{Y}}_i$  as the best. Also, form the confidence intervals

$$\min\{0, \overline{\overline{Y}}_i - \min_{i \neq i} \overline{\overline{Y}}_i - 2\} \le \theta_i - \min_{i \neq i} \theta_i \le \max\{0, \overline{\overline{Y}}_i - \min_{i \neq i} \overline{\overline{Y}}_i + 2\}$$

for i = 1, 2, 3, 4.

#### 12.2.3 Bonferroni Approach to Screening

When a two-stage procedure is not possible, or when there are many systems, it could be useful to divide the set of systems into those that could be the best and those that can be eliminated from further consideration. For this purpose, a screening or *subset selection* procedure is useful. The following procedure, due to Nelson *et al.* [2001], guarantees that the retained subset contains the true best system with probability  $\geq 1 - \alpha$  when the data are normally distributed and either independent sampling or CRN is used. The subset may contain all K of the systems, only one system, or some number in between, depending on the number of replications and the sample means and sample variances.

#### **Screening Procedure**

- 1. Specify the probability of correct selection  $1 \alpha$  and common sample size from each system,  $R \ge 2$ . Let  $t = t_{m(k) > R(k)}$

- **2.** Make R replications of system i to obtain  $Y_{1i}$ ,  $Y_{2i}$ ,  $Y_{Ri}$  for systems i = 1, 2, ..., K.

- **3.** Calculate the sample means  $\overline{Y}_i$  for i = 1, 2, ..., K. For all  $i \neq j$ , calculate the sample variance of the difference,

$$S_{ij}^{2} = \frac{1}{R-1} \sum_{i=1}^{R} (Y_{ri} - Y_{rj} - (\overline{Y}_{i} - \overline{Y}_{ij}))^{2}$$

**4.** If bigger is better, then retain system i in the selected subset if

$$\overline{Y}_i \ge \overline{Y}_j - t \frac{S_{ij}}{\sqrt{R}}$$

for all  $j \ne i$

If smaller is better, then retain system i in the selected subset if

$$\overline{Y}_{i} \le \overline{Y}_{ij} + t \frac{S_{ij}}{\sqrt{R}}$$

for all  $j \ne i$

All system designs that are not retained can be eliminated from further consideration.

#### **Example 12.4: Continued**

Suppose we want to see whether any of the designs for the vehicle-inspection station can be eliminated on the basis of only the 10 replications in Table 12.5. Summaries of the sample means and variances of the differences are as follows:

| $Y_{\cdot i}$ | 1     | 2     | 3                | 4                      |  |

|---------------|-------|-------|------------------|------------------------|--|

|               | 50.04 | 49.24 | 44.35            | 48.78                  |  |

| $S_{ij}^2$    | 1     | 2     | 3                | 4                      |  |

| 1<br>2<br>3   |       | 4.498 | 28.498<br>11.857 | 5.489<br>0.119<br>9.84 |  |

The appropriate critical value to obtain 95% confidence that the selected subset contains the true best is  $t = t_{0.0167,9} = 2.508$ . Recall that smaller response time is better. Applying the Subset Selection Procedure, system designs 1, 2, and 4 can all be eliminated, because

$$\overline{Y}_{1} = 50.04 \nleq \overline{Y}_{3} + t\sqrt{\frac{S_{13}^{2}}{R}} = 44.35 + 2.508\sqrt{\frac{28.498}{10}} = 48.58$$

$$\overline{Y}_{2} = 49.24 \nleq \overline{Y}_{3} + t\sqrt{\frac{S_{23}^{2}}{R}} = 44.35 + 2.508\sqrt{\frac{11.857}{10}} = 47.08$$

$$\overline{Y}_{4} = 48.78 \nleq \overline{Y}_{3} + t\sqrt{\frac{S_{43}^{2}}{R}} = 44.35 + 2.508\sqrt{\frac{9.84}{10}} = 46.84$$

Thus, in this case there was adequate data to select the best, system design 3, with 95% confidence. Had more than one system survived the subset selection, then we could perform additional analysis on that subset, perhaps using the Two-Stage Bonferroni Procedure.

#### 12.3 METAMODELING

Suppose that there is a simulation output response variable, Y, that is related to k independent variables, say  $x_1, x_2, \ldots, x_k$ . The dependent variable, Y, is a random variable, while the independent variables  $x_1, x_2, \ldots, x_k$  are called design variables and are usually subject to control. The true relationship between the variables Y and X is represented by the (often complex) simulation model. Our goal is to approximate this relationship by a simpler mathematical function called a metamodel. In some cases, the analyst will know the exact form of the functional relationship between Y and  $x_1, x_2, \ldots, x_k$ , say  $Y = f(x_1, x_2, \ldots, x_k)$ . However, in most cases, the functional relationship is unknown, and the analyst must select an appropriate f containing unknown parameters, and then estimate those parameters from a set of data (Y, x). Regression analysis is one method for estimating the parameters.

#### Example 12.5

An insurance company promises to process all claims it receives each day by the end of the next day. It has developed a simulation model of its proposed claims-processing system to evaluate how hard it will be to meet this promise. The actual number and types of claims that will need to be processed each day will vary, and the number may grow over time. Therefore, the company would like to have a model that predicts the total processing time as a function of the number of claims received.

The primary value of a metamodel is to make it easy to answer "what if" questions, such as, what the processing time will be if there are x claims. Evaluating a function f, or perhaps its derivatives, at a number of values of x is typically much easier than running a simulation experiment for each value.

#### 12.3.1 Simple Linear Regression

Suppose that it is desired to estimate the relationship between a single independent variable x and a dependent variable Y, and suppose that the true relationship between Y and x is suspected to be linear. Mathematically, the expected value of Y for a given value of x is assumed to be

$$E(Y \mid x) = \beta_0 + \beta_1 x \tag{12.21}$$

where  $\beta_0$  is the intercept on the Y axis, an unknown constant; and  $\beta_1$  is the slope, or change in Y for a unit change in x, also an unknown constant. It is further assumed that each observation of Y can be described by the model

$$Y = \beta_0 + \beta_1 x + \epsilon \tag{12.22}$$

where  $\epsilon$  is a random error with mean zero and constant variance  $\sigma^2$ . The regression model given by Equation (12.22) involves a single variable x and is commonly called a simple linear regression model.

Suppose that there are n pairs of observations  $(Y_1, x_1)$ ,  $(Y_2, x_2)$ , ..., $(Y_n, x_n)$ . These observations can be used to estimate  $\beta_0$  and  $\beta_1$  in Equation (12.22). The method of least squares is commonly used to form the estimates. In the method of least squares,  $\beta_0$  and  $\beta_1$  are estimated in such a way that the sum of the squares of the deviations between the observations and the regression line is minimized. The individual observations in Equation (12.22) can be written as

$$Y_i = \beta_0 + \beta_1 x_i + \epsilon_i, i = 1, 2, ..., n$$

(12.23)

where  $\epsilon_1, \epsilon_2 \dots$  are assumed to be uncorrelated random variables.

Each  $\epsilon_i$  in Equation (12.23) is given by

$$\epsilon_i = Y_i - \beta_0 - \beta_1 x_i \tag{12.24}$$

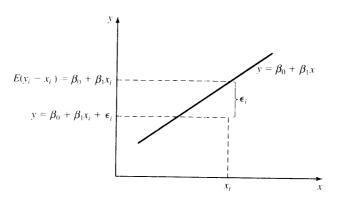

and represents the difference between the observed response,  $Y_i$ , and the expected response,  $\beta_0 + \beta_1 x_i$ , predicted by the model in Equation (12.21). Figure 12.3 shows how  $\epsilon_i$  is related to  $x_i, Y_i$ , and  $E(Y_i|x_i)$ .

The sum of squares of the deviations given in Equation (12.24) is given by

$$L = \sum_{i=1}^{n} \epsilon_i^2 = \sum_{i=1}^{n} (Y_i - \beta_0 - \beta_1 x_i)^2$$

(12.25)

and L is called the least-squares function. It is convenient to rewrite  $Y_i$  as follows:

$$Y_i = \beta_0' + \beta_1(x_i - \overline{x}) + \epsilon_i$$

(12.26)

where  $\beta_0' = \beta_0 + \beta_1 \overline{x}$  and  $\overline{x} = \sum_{i=1}^{n} x_i / n$ . Equation (12.26) is often called the transformed linear regression model. Using Equation (12.26), Equation (12.25) becomes

$$L = \sum_{i=1}^{n} [Y_i - \beta_0' - \beta_1 (x_i - \overline{x})]^2$$

To minimize L, find  $\partial L/\partial \beta_0'$  and  $\partial L/\partial \beta_1$ , set each to zero, and solve for  $\hat{\beta}_0'$  and  $\hat{\beta}_1$ . Taking the partial derivatives and setting each to zero yields

$$n\hat{\beta}'_{0} = \sum_{i=1}^{n} Y_{i}$$

$$\hat{\beta}_{1} \sum_{i=1}^{n} (x_{i} - \overline{x})^{2} = \sum_{i=1}^{n} Y_{i} (x_{i} - \overline{x})$$

(12.27)

Equations (12.27) are often called the "normal equations," which have the solutions

$$\hat{\beta}_0' = \overline{Y} = \sum_{i=1}^n \frac{Y_i}{n}$$

(12.28)

**Figure 12.3** Relationship of  $\epsilon_i$  to  $x_i$ ,  $Y_i$ , and  $E(Y_i | x_i)$ .

and

$$\hat{\beta}_{1} = \frac{\sum_{i=1}^{n} Y_{i}(x_{i} - \overline{x})}{\sum_{i=1}^{n} (x_{i} - \overline{x})^{2}}$$

(12.29)

The numerator in Equation (12.29) is rewritten for computational purposes as

$$S_{xy} = \sum_{i=1}^{n} Y_i(x_i - \overline{x}) = \sum_{i=1}^{n} x_i Y_i - \frac{\left(\sum_{i=1}^{n} x_i\right) \left(\sum_{i=1}^{n} Y_i\right)}{n}$$

(12.30)

where  $S_{xy}$  denotes the corrected sum of cross products of x and Y. The denominator of Equation (12.29) is rewritten for computational purposes as

$$S_{xx} = \sum_{i=1}^{n} (x_i - \overline{x})^2 = \sum_{i=1}^{n} x_i^2 - \frac{\left(\sum_{i=1}^{n} x_i\right)^2}{n}$$

(12.31)

where  $S_{xx}$  denotes the corrected sum of squares of x. The value of  $\hat{\beta}_0$  can be retrieved easily as

$$\hat{\beta}_0 = \hat{\beta}_0' - \hat{\beta}_1 \overline{x} \tag{12.32}$$

#### Example 12.6: Calculating $\hat{\beta}_0$ and $\hat{\beta}_1$

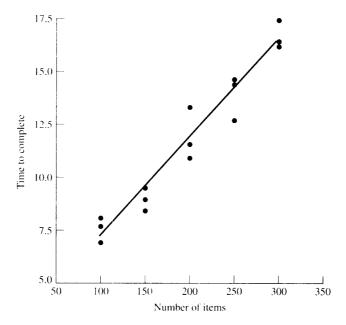

The simulation model of the claims-processing system in Example 12.5 was executed with initial conditions x = 100, 150, 200, 250, and 300 claims received the previous day. Three replications were obtained at each setting. The response Y is the number of hours required to process x claims. The results are shown in Table 12.8. The graphical relationship between the number of claims received and total processing time is shown in

**Table 12.8** Simulation Results for Processing Time Given x Claims

| Number of Claims x | Hours of Processing Time Y |

|--------------------|----------------------------|

| 100                | 8.1                        |

| 100                | 7.8                        |

| 100                | 7.0                        |

| 150                | 9.6                        |

| 150                | 8.5                        |

| 150                | 9.0                        |

| 200                | 10.9                       |

| 200                | 13.3                       |

| 200                | 11.6                       |

| 250                | 12.7                       |

| 250                | 14.5                       |

| 250                | 14.7                       |

| 300                | 16.5                       |

| 300                | 17.5                       |

| 300                | 16.3                       |

**Figure 12.4** Relationship between number of claims and hours of processing time.

Figure 12.4. Such a display is called a scatter diagram. Examination of this scatter diagram indicates that there is a strong relationship between number of claims and processing time. The tentative assumption of the linear model given by Equation (12.22) appears to be reasonable.

With the processing times as the  $Y_i$  values (the dependent variables) and the number of claims as the  $x_i$  values (the independent variables),  $\hat{\beta}_0$  and  $\hat{\beta}_1$  can be found by the following computations: n = 15,  $\sum_{i=1}^{15} x_i = 3000$ ,  $\sum_{i=1}^{15} X_i^2 = 675,000$ ,  $\sum_{i=1}^{15} x_i^2 = 39080$ , and  $\overline{x} = 3000/15 = 200$ .

From Equation (12.30)  $S_{yy}$  is calculated as

$$S_{xy} = 39,080 - \frac{(3000)(178)}{15} = 3480$$

From Equation (12.31),  $S_{rr}$  is calculated as

$$S_{xx} = 675,000 - \frac{(3000)^2}{15} = 75,000$$

Then,  $\hat{\beta}_{\mathbf{l}}$  is calculated from Equation (12.29) as

$$\hat{\beta}_1 = \frac{S_{yy}}{S_{yy}} = \frac{3480}{75,000} = 0.0464$$

As shown in Equation (12.28),  $\hat{\beta}'_0$  is just  $\bar{Y}$ , or

$$\hat{\beta}_0' = \frac{178}{15} \approx 11.8667$$

To express the model in the original terms, compute  $\hat{\beta}_0$  from Equation (12.32) as

$$\hat{\beta}_0 = 11.8667 - 0.0464(200) = 2.5867$$

Then an estimate of the mean of Y given x, E(Y|x), is given by

$$\hat{y} = \hat{\beta}_0 + \hat{\beta}_1 x = 2.5867 + 0.0464x \tag{12.33}$$

For a given number of claims, x, this model can be used to predict the number of hours required to process them. The coefficient  $\hat{\beta}_1$  has the interpretation that each additional claim received adds an expected 0.0464 hours, or 2.8 minutes, to the expected total processing time.

Regression analysis is widely used and frequently misused. Several of the common abuses are briefly mentioned here. Relationships derived in the manner of Equation (12.33) are valid for values of the independent variable within the range of the original data. The linear relationship that has been tentatively assumed may not be valid outside the original range. In fact, we know from queueing theory that mean processing time may increase rapidly as the number of claims approaches the capacity of the system. Therefore, Equation (12.33) can be considered valid only for  $100 \le x \le 300$ . Regression models are not advised for extrapolation purposes.

Care should be taken in selecting variables that have a plausible causal relationship with each other. It is quite possible to develop statistical relationships that are unrelated in a practical sense. For example, an attempt might be made to relate monthly output of a steel mill to the weight of reports appearing on a manager's desk during the month. A straight line may appear to provide a good model for the data, but the relationship between the two variables is tenuous. A strong observed relationship does not imply that a causal relationship exists between the variables. Causality can be inferred only when analysis uncovers some plausible reasons for its existence. In Example 12.5 it is reasonable that starting with more claims implies that more time is needed to process them. Therefore, a relationship of the form of Equation (12.33) is at least plausible.

#### 12.3.2 Testing for Significance of Regression

In Section 12.3.1, it was assumed that a linear relationship existed between Y and x. In Example 12.5, a scatter diagram, shown in Figure 12.4, relating number of claims and processing time was prepared to evaluate whether a linear model was a reasonable tentative assumption prior to the calculation of  $\hat{\beta}_0$  and  $\hat{\beta}_1$ . However, the adequacy of the simple linear relationship should be tested prior to using the model for predicting the response,  $Y_i$ , given an independent variable,  $x_i$ . There are several tests which may be conducted to aid in determining model adequacy. Testing whether the order of the model tentatively assumed is correct, commonly called the "lack-of-fit test," is suggested. The procedure is explained by Box and Draper [1987], Hines, Montgomery, Goldsman, and Borror [2002], and Montgomery [2000].

Testing for the significance of regression provides another means for assessing the adequacy of the model. The hypothesis test described next requires the additional assumption that the error component  $\epsilon_i$  is normally distributed. Thus, the complete assumptions are that the errors are NID(0,  $\sigma^2$ )—that is, normally and independently distributed with mean zero and constant variance  $\sigma^2$ . The adequacy of the assumptions can and should be checked by residual analysis, discussed by Box and Draper [1987], Hines, Montgomery, Goldsman, and Borror [2002], and Montgomery |2000].

Testing for significance of regression is one of many hypothesis tests that can be developed from the variance properties of  $\hat{\beta}_0$  and  $\hat{\beta}_1$ . The interested reader is referred to the references just cited for extensive discussion of hypothesis testing in regression. Just the highlights of testing for significance of regression are given in this section.

Suppose that the alternative hypotheses are

$$H_0: \beta_1 = 0$$

$$H_1: \beta_1 \neq 0$$

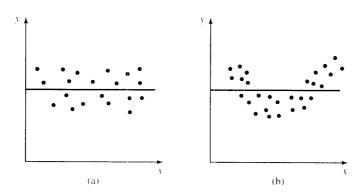

Failure to reject  $H_0$  indicates that there is no linear relationship between x and Y. This situation is illustrated in Figure 12.5. Notice that two possibilities exist. In Figure 12.5(a), the implication is that x is of little value in explaining the variability in Y, and that  $\hat{y} = \overline{Y}$  is the best estimator. In Figure 12.5(b), the implication is that the true relationship is not linear.

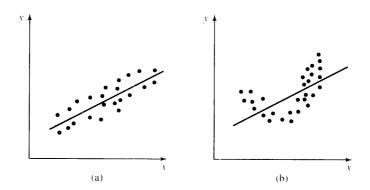

Alternatively, if  $H_0$  is rejected, the implication is that x is of value in explaining the variability in Y. This situation is illustrated in Figure 12.6. Here, also, two possibilities exist. In Figure 12.6(a), the straight-line model is adequate. However, in Figure 12.6(b), even though there is a linear effect of x, a model with higher-order terms (such as  $x^2$ ,  $x^3$ , ...) is necessary. Thus, even though there may be significance of regression, testing of the residuals and testing for lack of fit are needed to confirm the adequacy of the model.

The appropriate test statistic for significance of regression is given by

$$t_0 = \frac{\hat{\beta}_1}{\sqrt{MS_E/S_{xx}}} \tag{12.34}$$

**Figure 12.5** Failure to reject  $H_0: \beta_1 = 0$ .

**Figure 12.6**  $H_0: \beta_1 = 0$  is rejected.

where  $MS_E$  is the mean squared error. The error is the difference between the observed value,  $Y_i$ , and the predicted value,  $\hat{y}_i$ , at  $x_i$ , or  $e_i = Y_i - \hat{y}_i$ . The squared error is given by  $\sum_{i=1}^n e_i^2$ , and the mean squared error, given by

$$MS_E = \sum_{i=1}^{n} \frac{e_i^2}{n-2}$$

(12.35)

is an unbiased estimator of  $\sigma^2 = V(\epsilon_i)$ . The direct method can be used to calculate  $\sum_{i=1}^n e_i^2$ : Calculate each  $\hat{y}_i$ , compute  $e_i^2$ , and sum all the  $e_i^2$  values, i = 1, 2, ..., n. However, it can be shown that

$$\sum_{i=1}^{n} e_{i}^{2} = S_{yy} - \hat{\beta}_{1} S_{xy}$$

(12.36)

where  $S_{yy}$ , the corrected sum of squares of Y, is given by

$$S_{yy} = \sum_{i=1}^{n} Y_i^2 - \frac{\left(\sum_{i=1}^{n} Y_i\right)^2}{n}$$

(12.37)

and  $S_{xy}$  is given by Equation (12.30). Equation (12.36) could be easier to use than the direct method.

The statistic defined by Equation (12.34) has the t distribution with n-2 degrees of freedom. The null hypothesis  $H_0$  is rejected if  $|t_0| > t_{\alpha/2, n-2}$ .

#### **Example 12.7: Testing for Significance of Regression**

Given the results in Example 12.6, the test for the significance of regression is conducted. One more computation is needed prior to conducting the test. That is,  $\sum_{i=1}^{n} Y_i^2 = 2282.94$ . Using Equation (12.37) yields

$$S_{yy} = 2282.94 - \frac{(178)^2}{15} = 170.6734$$

Then  $\sum_{i=1}^{15} e_i^2$  is computed according to Equation (12.36) as

$$\sum_{i=1}^{15} e_i^2 = 170.6734 - 0.0464(3480) = 9.2014$$

Now, the value of  $MS_E$  is calculated from Equation (12.35):

$$MS_E = \frac{9.2014}{13} = 0.7078$$

The value of  $t_0$  can be calculated by using Equation (12.34) as

$$t_0 = \frac{0.0464}{\sqrt{0.7078/75000}} = 15.13$$

Since  $t_{0.025,13} = 2.16$  from Table A.5, we reject the hypothesis that  $\beta_1 = 0$ . Thus, there is significant evidence that x and Y are related.

#### 12.3.3 Multiple Linear Regression

If the simple linear regression model of Section 12.3.1 is inadequate, several other possibilities exist. There could be several independent variables, so that the relationship is of the form

$$Y = \beta_0 + \beta_1 x_1 + \beta_2 x_2 + \dots + \beta_m x_m + \epsilon$$

(12.38)

Notice that this model is still linear, but has more than one independent variable. Regression models having the form shown in Equation (12.38) are called multiple linear regression models. Another possibility is that the model is of a quadratic form such as

$$Y = \beta_0 + \beta_1 x + \beta_2 x^2 + \epsilon \tag{12.39}$$

Equation (12.39) is also a linear model which may be transformed to the form of Equation (12.38) by letting  $x_1 = x$  and  $x_2 = x^2$ .

Yet another possibility is a model of the form such as

$$Y = \beta_0 + \beta_1 x_1 + \beta_2 x_2 + \beta_3 x_1 x_3 + \epsilon$$

which is also a linear model. The analysis of these three models with the forms just shown, and related models, can be found in Box and Draper [1987]. Hines, Montgomery, Goldsman, and Borror [2002]. Montgomery [2000], and other applied statistics texts; and also in Kleijnen [1987, 1998], which is concerned primarily with the application of these models in simulation.

#### 12.3.4 Random-Number Assignment for Regression

The assignment of random-number seeds or streams is part of the design of a simulation experiment.<sup>4</sup> Assigning a different seed or stream to different design points (settings for  $x_1, x_2, \dots x_m$  in a multiple linear regression) guarantees that the responses Y from different design points will be statistically independent. Similarly, assigning the same seed or stream to different design points induces dependence among the corresponding responses, by virtue of their all having the same source of randomness.

Many textbook experimental designs assume independent responses across design points. To conform to this assumption, we must assign different seeds or streams to each design point. However, it is often useful to assign the same random number seeds or streams to all of the design points—in other words, to use common random numbers.

The intuition behind common random numbers for metamodels is that a fairer comparison among design points is achieved if the design points are subjected to the same experimental conditions, specifically the same source of randomness. The mathematical justification is as follows: Suppose we fit the simple linear regression  $Y_i = \beta_0 + \beta_1 x_i + \epsilon_i$  and obtain least squares estimates  $\hat{\beta}_0$  and  $\hat{\beta}_1$ . Then an estimator of the expected difference in performance between design points i and j is

$$\hat{\beta}_0 + \hat{\beta}_1 x_i - (\hat{\beta}_0 + \hat{\beta}_1 x_i) = \hat{\beta}_1 (x_i - x_i)$$

when  $x_i$  and  $x_j$  are fixed design points,  $\hat{\beta}_1$  determines the estimated difference between design points i and j, or for that matter between any other two values of x. Therefore, common random numbers can be expected to reduce the variance of  $\hat{\beta}_1$  and, more generally, reduce the variance of all of the slope terms in a multiple linear regression. Common random numbers typically do not reduce the variance of the intercept term,  $\hat{\beta}_0$ .

<sup>&</sup>lt;sup>4</sup>This section is based on Nelson [1992].

The least-squares estimators  $\hat{\beta}_0$  and  $\hat{\beta}_1$  are appropriate regardless of whether we use common random numbers, but the associated statistical analysis is affected by that choice. For statistical analysis of a metamodel under common random numbers, see Kleijnen [1988] and Nelson [1992].

#### 12.4 OPTIMIZATION VIA SIMULATION

| Consider the following examples. <sup>5</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

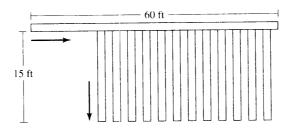

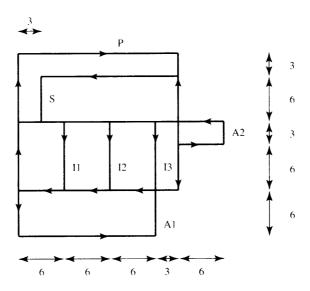

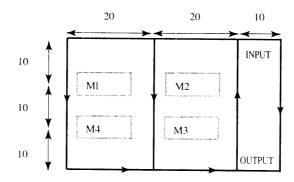

| Example 12.8: Materials Handling System (MHS)  Engineers need to design a MHS consisting of a large automated storage and retrieval device, automated guided vehicles (AGVs), AGV stations, lifters, and conveyors. Among the design variables they can contro are the number of AGVs, the load per AGV, and the routing algorithm used to dispatch the AGVs Alternative designs will be evaluated according to AGV utilization, transportation delay for material that needs to be moved, and overall investment and operation costs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Example 12.9: Liquified Natural Gas (LNG) Transportation  A LNG transportation system will consist of LNG tankers and of loading, unloading, and storage facilities In order to minimize cost, designers can control tanker size, number of tankers in use, number of jetties a the loading and unloading facilities, and capacity of the storage tanks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example 12.10: Automobile Engine Assembly  In an assembly line, a large buffer (queue) between workstations could increase station utilization—because there will tend to be something waiting to be processed—but drive up space requirements and work-in-process inventory. An allocation of buffer capacity that minimizes the sum of these competing costs is desired.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Example 12.11: Traffic Signal Sequencing  Civil engineers want to sequence the traffic signals along a busy section of road to reduce driver delay and the congestion occurring along narrow cross streets. For each traffic signal, the length of the red, green, and green-turn-arrow cycles can be set individually.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

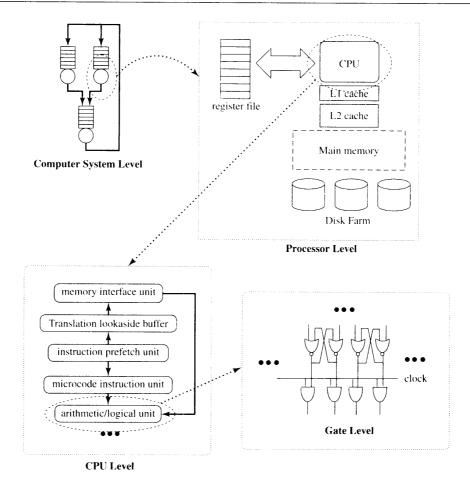

| Example 12.12: On-Line Services  A company offering on-line information services over the Internet is changing its computer architecture from central mainframe computers to distributed workstation computing. The numbers and types of CPUs, the network structure, and the allocation of processing tasks all need to be chosen. Response time to custome queries is the key performance measure.  What do these design problems have in common? Clearly, a simulation model could be useful in each and all have an implied goal of finding the best design relative to some performance measures (cost, delay etc.). In each example, there are potentially a very large number of alternative designs, ranging from tens to thousands, and certainly more than the 2 to 10 we considered in Section 12.2.2. Some of the examples contain a diverse collection of decision variables: discrete (number of AGVs, number of CPUs), continuou (tanker size, red-cycle length) and qualitative (routing strategy, algorithm for allocating processing tasks). |

All of these problems fall under the general topic of "optimization via simulation," where the goal is to minimize or maximize some measures of system performance and system performance can be evaluated only by running a computer simulation. Optimization via simulation is a relatively new, but already vast, topic, and commercial software has become widely available. In this section, we describe the key issues that should be considered in undertaking optimization via simulation, provide some pointers to the available literature.

and give one example algorithm.

This makes developing a metamodel, as described in Section 12.3, difficult.

Some of these descriptions are based on Boesel, Nelson, and Ishii [2003].

#### 12.4.1 What Does 'Optimization via Simulation' Mean?

Optimization is a key tool used by operations researchers and management scientists, and there are well-developed algorithms for many classes of problems, the most famous being linear programming. Much of the work on optimization deals with problems in which all aspects of the system are treated as being known with certainty; most critically, the performance of any design (cost, profit, makespan, etc.) can be evaluated exactly.

In stochastic, discrete-event simulation, the result of any simulation run is a random variable. For notation, let  $x_1, x_2, ..., x_m$  be the *m* controllable design variables and let  $Y(x_1, x_2, ..., x_m)$  be the observed simulation output performance on one run. To be concrete,  $x_1, x_2, x_3$  might denote the number of AGVs, the load per AGV, and the routing algorithm used to dispatch the AGVs, respectively, in Example 12.8, while  $Y(x_1, x_2, x_3)$  could be total MHS acquisition and operation cost.

What does it mean to "optimize"  $Y(x_1, x_2, ..., x_m)$  with respect to  $x_1, x_2, ..., x_m$ ? Y is a random variable, so we cannot optimize the *actual* value of Y. The most common definition of optimization is

maximize or minimize

$$E(Y(x_1, x_2, ..., x_m))$$

(12.40)

In other words, the mathematical expectation, or long-run average, of performance is maximized or minimized. This is the default definition of optimization used in all commercial packages of which we are aware. In our example,  $E(Y(x_1, x_2, x_3))$  is the expected, or long-run average cost of operating the MHS with  $x_1$  AGVs,  $x_2$ , load per AGV, and routing algorithm  $x_3$ .

It is important to note that (12.40) is not the only possible definition, however. For instance, we might want to select the MHS design that has the best chance of costing less than D to purchase and operate, changing the objective to

maximize Pr

$$(Y(x_1, x_2, x_3) \le D)$$

We can fit this objective into formulation (12.40) by defining a new performance measure

$$Y'(x_1, x_2, x_3) = \begin{cases} 1, & \text{if } Y(x_1, x_2, x_3) \le D \\ 0, & \text{otherwise} \end{cases}$$

and maximizing  $E\left(Y'(x_1, x_2, x_3)\right)$  instead.

A more complex optimization problem occurs when we want to select the system design that is *most likely* to be the best. Such an objective is relevant when one-shot, rather than long-run average, performance matters. Examples include a Space Shuttle launch, or the delivery of a unique, large order of products. Bechhofer, Santner, and Goldsman [1995] address this problem under the topic of "multinomial selection."

We have been assuming that a system design  $x_1, x_2, \dots, x_m$  can be evaluated in terms of a single performance measure, Y, such as cost. Obviously, this may not always be the case. In the MHS example, we might also be interested in some measure of system productivity, such as throughput or cycle time. At present, multiple objective optimization via simulation is not well developed. Therefore, one of three strategies is typically employed:

- Combine all of the performance measures into a single measure, the most common being cost. For

instance, the revenue generated by each completed product in the MHS could represent productivity

and be included as a negative cost.

- 2. Optimize with respect to one key performance measure, but then evaluate the top solutions with respect to secondary performance measures. For instance, the MHS could be optimized with respect to expected cost, and then the cycle time could be compared for the top 5 designs. This approach requires that information on more than just the best solution be maintained.

3. Optimize with respect to one key performance measure, but consider only those alternatives that meet certain constraints on the other performance measures. For instance, the MHS could be optimized with respect to expected cost for those alternatives whose expected cycle time is less than a given threshold.

#### 12.4.2 Why is Optimization via Simulation Difficult?

Even when there is no uncertainty, optimization can be very difficult if the number of design variables is large, the problem contains a diverse collection of design variable types, and little is known about the structure of the performance function. Optimization via simulation adds an additional complication: The performance of a particular design cannot be evaluated exactly, but instead must be estimated. Because we have estimates, it is not possible to conclude with assurance that one design is better than another, and this uncertainty frustrates optimization algorithms that try to move in improving directions. In principle, one can eliminate this complication by making so many replications, or such long runs, at each design point that the performance estimate has essentially no variance. In practice, this could mean that very few alternative designs will be explored, because of the time required to simulate each one.

The existence of sampling variability forces optimization via simulation to make compromises. The following are the standard ones:

- Guarantee a prespecified probability of correct selection. The Two-Stage Bonferroni Procedure in Section 12.2.2 is an example of this approach, which allows the analyst to specify the desired chance of being right. Such algorithms typically require either that every possible design be simulated or that a strong functional relationship among the designs (such as a metamodel) apply. Other algorithms can be found in Goldsman and Nelson [1998].

- Guarantee asymptotic convergence. There are many algorithms that guarantee convergence to the global optimal solution as the simulation effort (number of replications, length of replications) becomes infinite. These guarantees are useful because they indicate that the algorithm tends to get to where the analyst wants it to go. However, convergence can be slow, and there is often no guarantee as to how good the reported solution is when the algorithm is terminated in finite time (as it must be in practice). See Andradóttir [1998] for specific algorithms that apply to discrete- or continuous-variable problems.

- Optimal for deterministic counterpart. The idea here is to use an algorithm that would find the optimal solution if the performance of each design could be evaluated with certainty. An example might be applying a standard nonlinear programming algorithm to the simulation optimization problem. It is typically up to the analyst to make sure that enough simulation effort is expended (replications or run length) to insure that such an algorithm is not misled by sampling variability. Direct application of an algorithm that assumes deterministic evaluation to a stochastic simulation is not recommended.

- Robust heuristics. Many heuristics have been developed for deterministic optimization problems that do not guarantee finding the optimal solution, but nevertheless been shown to be very effective on difficult, practical problems. Some of these heuristics use randomness as part of their search strategy, so one might argue that they are less sensitive to sampling variability than other types of algorithms. Nevertheless, it is still important to make sure that enough simulation effort is expended (replications or run length) to insure that such an algorithm is not misled by sampling variability.

Robust heuristics are the most common algorithms found in commercial optimization via simulation software. We provide some guidance on their use in the next section. See Fu [2002] for a comprehensive discussion of optimization theory versus practice.

#### 12.4.3 Using Robust Heuristics

By a "robust heuristic" we mean a procedure that does not depend on strong problem structure—such as continuity or convexity of  $E(Y(x_1, ..., x_m))$ —to be effective, can be applied to problems with mixed types of decision variables, and—ideally—is tolerant of some sampling variability. Genetic algorithms (GA) and tabu search (TS) are two prominent examples, but there are many others and many variations of them. Such heuristics form the core of most commercial implementations. To give a sense of these heuristics, we describe GA and TS next. We caution the reader that only a high-level description of the simplest version of each procedure is provided. The commercial implementations are much more sophisticated.

Suppose that there are k possible solutions to the optimization via simulation problem. Let  $\mathbf{X} = \{\mathbf{x}_1, \mathbf{x}_2, \dots, \mathbf{x}_k\}$  denote the solutions, where the ith solution  $\mathbf{x}_i = (x_{i1}, x_{i2}, \dots, x_{im})$  provides specific settings for the m decision variables. The simulation output at solution  $\mathbf{x}_i$  is denoted  $Y(\mathbf{x}_i)$ ; this could be the output of a single replication, or the average of several replications. Our goal is to find the solution  $\mathbf{x}^*$  that minimizes  $E(Y(\mathbf{x}))$ .

On each iteration (known as a "generation"). a GA operates on a "population" of p solutions. Denote the population of solutions on the jth iteration as  $\mathbf{P}(j) = \{\mathbf{x}_1(j), \mathbf{x}_2(j), ..., \mathbf{x}_p(j)\}$ . There may be multiple copies of the same solution in  $\mathbf{P}(j)$ , and  $\mathbf{P}(j)$  may contain solutions that were discovered on previous iterations. From iteration to iteration, this population evolves in such a way that good solutions tend to survive and give birth to new, and hopefully better, solutions, while inferior solutions tend to be removed from the population. The basic GA is given here:

#### **Basic GA**

**Step 1.** Set the iteration counter j = 0, and select (perhaps randomly) an initial population of p solutions  $\mathbf{P}(0) = \{\mathbf{x}_1(0), ..., \mathbf{x}_p(0)\}.$

**Step 2.** Run simulation experiments to obtain performance estimates  $Y(\mathbf{x})$  for all p solutions  $\mathbf{x}(j)$  in  $\mathbf{P}(j)$ .

**Step 3.** Select a population of p solutions from those in P(j) in such a way that those with smaller Y(x) values are more likely, but not certain, to be selected. Denote this population of solutions as P(j + 1).

**Step 4.** Recombine the solutions in P(j + 1) via crossover (which joins parts of two solutions  $\mathbf{x}_i(j + 1)$  and  $\mathbf{x}_i(j + 1)$  to form a new solution) and mutation (which randomly changes a part of a solution  $\mathbf{x}_i(j + 1)$ .

**Step 5.** Set j = j + 1 and go to Step 2.

The GA can be terminated after a specified number of iterations, when little or no improvement is noted in the population, or when the population contains p copies of the same solution. At termination, the solution  $\mathbf{x}^*$  that has the smallest  $Y(\mathbf{x})$  value in the last population is chosen as best (or alternatively, the solution with the smallest  $Y(\mathbf{x})$  over all iterations could be chosen).

GAs are applicable to almost any optimization problem, because the operations of selection, crossover, and mutation can be defined in a very generic way that does not depend on specifics of the problem. However, when these operations are not tuned to the specific problem, a GA's progress can be very slow. Commercial versions are often self-tuning, meaning that they update selection, crossover, and mutation parameters during the course of the search. There is some evidence that GAs are tolerant of sampling variability in  $Y(\mathbf{x})$  because they maintain a population of solutions rather than focusing on improving a current-best solution. In other words, it is not critical that the GA rank the solutions in a population of solutions perfectly, because the next iteration depends on the entire population, not on a single solution.

TS, on the other hand, identifies a current best solution on each iteration and then tries to improve it. Improvements occur by changing the solution via "moves." For example, the solution  $(x_1, x_2, x_3)$  could be changed

to the solution  $(x_1 + 1, x_2, x_3)$  by the move of adding 1 to the first decision variable (perhaps  $x_1$  represents the number of AGVs in Example 12.8, so the move would add one more AGV). The "neighbors" of solution  $\mathbf{x}$  are all of those solutions that can be reached by legal moves. TS finds the best neighbor solution and moves to it. However, to avoid making moves that return the search to a previously visited solution, moves may become "tabu" (not usable) for some number of iterations. Conceptually, think about how you would find your way through a maze: If you took a path that lead to a dead end, then you would avoid taking that path again (it would be tabu).

The basic TS algorithm is given next. The description is based on Glover [1989].

#### **Basic TS**

**Step 1.** Set the iteration counter j = 0 and the list of tabu moves to empty. Select an initial solution  $\mathbf{x}^*$  in  $\mathbf{X}$  (perhaps randomly).

**Step 2.** Find the solution  $\mathbf{x}'$  that minimizes  $Y(\mathbf{x})$  over all of the neighbors of  $\mathbf{x}^*$  that are not reached by tabu moves, running whatever simulations are needed to do the optimization.

**Step 3.** If  $Y(\mathbf{x}') < Y(\mathbf{x}^*)$ , then  $x^* = x'$  (move the current best solution to x').

**Step 4.** Update the list of tabu moves and go to Step 2.

The TS can be terminated when a specified number of iterations have been completed, when some number of iterations has passed without changing  $\mathbf{x}^*$ , or when there are no more feasible moves. At termination, the solution  $\mathbf{x}^*$  is chosen as best.

TS is fundamentally a discrete-decision-variable optimizator, but continuous decision variables can be discretized, as described in Section 12.4.4. TS aggressively pursues improving solutions, and therefore tends to make rapid progress. However, it is more sensitive to random variability in  $Y(\mathbf{x})$ , because  $\mathbf{x}^*$  is taken to be the *true* best solution so far and attempts are made to improve it. There are probabilistic versions of TS that should be less sensitive, however. An important feature of commercial implementations of TS, which is not present in the Basic TS, is a mechanism for overiding the tabu list when doing so is advantageous.

Next, we offer two suggestions for using commercial products that employ a GA. TS, or other robust heuristic controlling sampling variability, and *restarting*.

#### **Control Sampling Variability**

In many cases, it will up to the user to determine how much sampling (replications or run length) will be undertaken at each potential solution. This is a difficult problem in general. Ideally, sampling should increase as the heuristic closes in on the better solutions, simply because it is much more difficult to distinguish solutions that are close in expected performance from those that differ widely. Early in the search, it may be easy for the heuristic to identify good solutions and search directions, because clearly inferior solutions are being compared to much better ones, but late in the search this might not be the case.

If the analyst must specify a fixed number of replications per solution that will be used through the search, then a preliminary experiment should be conducted. Simulate several designs, some at the extremes of the solution space and some nearer the center. Compare the apparent best and apparent worst of these designs, using the approaches in Section 12.1. Using the technique described in Section 12.1.4, find the minimum for the number of replications required to declare these designs to be statistically significantly different. This is the minimum number of replications that should be used.

After the optimization run has completed, perform a second set of experiments on the top 5 to 10 designs identified by the heuristic. Use the comparison techniques in Section 12.2–12.2.3 to rigorously evaluate which are the best or near-best of these designs.

#### Restarting

Because robust heuristics provide no guarantees that they converge to the optimal solution for optimization via simulation, it makes sense to run the optimization two or more times to see which run yields the best solution. Each optimization run should use different random number seeds or streams and, ideally, should start from different initial solutions. Try starting the optimization at solutions on the extremes of the solution space, in the center of the space and at randomly generated solutions. If people familiar with the system suspect that certain designs will be good, be sure to include them as possible starting solutions for the heuristic.

#### 12.4.4 An Illustration: Random Search

In this section, we present an algorithm for optimization via simulation known as random search. The specific implementation is based on Algorithm 2 in Andradóttir [1998], which provides guaranteed asymptotic convergence under certain conditions. Thus, it will find the true optimal solution if permitted to run long enough. However, in practice, convergence can be slow, and the memory requirements of this particular version of random search can be quite large. Even though random search is not a "robust heuristic," we will also use it to demonstrate some strategies we would employ in conjunction with such heuristics and to demonstrate why optimization via simulation is tricky even with what appears to be an uncomplicated algorithm.

The random-search algorithm that we present requires that there be a finite number of possible system designs (although that number may be quite large). This might seem to rule out problems with continuous decision variables, such as conveyor speed. In practice, however, apparently continuous decision variables can often be discretized in a reasonable way. For instance, if conveyor speed can be anything from 60 to 120 feet per minute, little may be lost by treating the possible conveyor speeds as 60, 61, 62, ..., 120 feet per minute (61 possible values). Note, however, that there are algorithms designed specifically for continuous-variable problems (Andradóttir [1998]).

Again, let the k possible solutions to the optimization via simulation problem be denoted  $\{\mathbf{x}_1, \mathbf{x}_2, ..., \mathbf{x}_k\}$ , where the ith solution  $\mathbf{x}_i = (x_{i1}, x_{i2}, ..., x_{im})$  provides specific settings for the m decision variables. The simulation output at solution  $\mathbf{x}_i$  is denoted  $Y(\mathbf{x}_i)$ ; this could be the output of a single replication or the average of several replications. Our goal is to find the solution  $\mathbf{x}^*$  that minimizes  $E(Y(\mathbf{x}))$ .

On each iteration of the random-search algorithm, we compare a current good solution to a randomly chosen competitor. If the competitor is better, then it becomes the current good solution. When we terminate the search, the solution we choose is the one that has been visited most often (which means that we expect to revisit solutions many times).

#### Random-Search Algorithm

- **Step 1.** Initialize counter variables C(i) = 0 for i = 1, 2, ..., k. Select an initial solution  $i^0$ , and set  $C(i^0) = 1$ . C(i) counts the number of times we visit solution i.

- **Step 2.** Choose another solution i' from the set of all solutions except  $i^0$  in such a way that each solution has an equal chance of being selected.

- **Step 3.** Run simulation experiments at the two solutions  $i^0$  and i' to obtain outputs  $Y(i^0)$  and Y(i'). If  $Y(i') < Y(i^0)$ , then set  $i^0 = i'$ . (See note following Step 4.)

- **Step 4.** Set  $C(i^0) = C(i^0) + 1$ . If not done, then go to Step 2. If done, then select as the estimated optimal solution  $xi^*$  such that  $C(i^*)$  is the largest count.

Note that, if the problem is a maximization problem, then replace Step 3 with

**Step 3.** Run simulation experiments at the two solutions  $i^0$  and i' to obtain outputs  $Y(i^0)$  and Y(i'). If  $Y(i') > Y(i^0)$ , then set  $i^0 = i'$ .

One of the difficult problems with many optimization-via-simulation algorithms is knowing when to stop. (Exceptions include algorithms that guarantee a probability of correct selection.) Typical rules might be to stop after a certain number of iterations, stop when the best solution has not changed much in several iterations, or stop when all time available to solve the problem has been exhausted. Whatever rule is used, we recommend applying a statistical selection procedure, such as the Two-Stage Bonferroni Procedure in Section 12.2.2, to the 5 to 10 apparently best solutions. This is done to evaluate which among them is the true best with guaranteed confidence. If the raw data from the search have been saved, then these data can be used as the first-stage sample for a two-stage selection procedure (Boesel, Nelson, and Ishii [2003]).

#### **Example 12.13: Implementing Random Search**

Suppose that a manufacturing system consists of 4 stations in series. The zeroth station always has raw material available. When the zeroth station completes work on a part, it passes the part along to the first station, then the first passes the part to the second, and so on. Buffer space between stations 0 and 1, 1 and 2, and 2 and 3 is limited to 50 parts total. If, say, station 2 finishes a part but there is no buffer space available in front of station 3, then station 2 is blocked, meaning that it cannot do any further work. The question is how to allocate these 50 spaces to minimize the expected cycle time per part over one shift.

Let  $x_i$  be the number of buffer spaces in front of station *i*. Then the decision variables are  $x_1, x_2, x_3$  with the constraint that  $x_1 + x_2 + x_3 = 50$  (it makes no sense to allocate fewer buffer spaces than we have available). This implies a total of 1326 possible designs (can you figure out how this number is computed?).

To simplify the presentation of the random-search algorithm, let the counter for solution  $(x_1, x_2, x_3)$  be denoted as  $C(x_1, x_2, x_3)$ .

#### Random Search Algorithm

- **Step 1.** Initialize 1326 counter variables  $C(x_1, x_2, x_3) = 0$ , one for each of the possible solutions  $(x_1, x_2, x_3)$ . Select an initial solution, say  $(x_1 = 20, x_2 = 15, x_3 = 15)$  and set C(20, 15, 15) = 1.

- **Step 2.** Choose another solution from the set of all solutions *except* (20, 15, 15) in such a way that each solution has an equal chance of being selected. Suppose (11, 35, 4) is chosen.

- **Step 3.** Run simulation experiments at the two solutions to obtain estimates of the expected cycle time Y(20, 15, 15) and Y(11, 35, 4). Suppose that Y(20, 15, 15) < Y(11, 35, 4). Then (20, 15, 15) remains as the current good solution.

- **Step 4.** Set C(20, 15, 15) = C(20, 15, 15) + 1.

- **Step 2.** Choose another solution from the set of all solutions *except* (20, 15, 15) in such a way that each solution has an equal chance of being selected. Suppose (28, 12, 10) is chosen.

- **Step 3.** Run simulation experiments at the two solutions to obtain estimates of the expected cycle time Y(20, 15, 15) and Y(28, 12, 10). Suppose that Y(28, 12, 10) < Y(20, 15, 15). Then (28, 12, 10) becomes the current good solution.

- **Step 4.** Set C(28, 12, 10) = C(28, 12, 10) + 1.

- **Step 2.** Choose another solution from the set of all solutions *except* (28, 12, 10) in such a way that each solution has an equal chance of being selected. Suppose (0, 14, 36) is chosen.

#### Step 3. Continue...

When the search is terminated, we select the solution  $(x_1, x_2, x_3)$  that gives the largest  $C(x_1, x_2, x_3)$  count. As we discussed earlier, the top 5 to 10 solutions should then be subjected to a separate statistical analysis to determine which among them is the true best (with high confidence). In this case, the solutions with the largest counts would receive the second analysis.

Despite the apparent simplicity of the Random-Search Algorithm, we have glossed over a subtle issue that often arises in algorithms with provable performance. In Step 2, the algorithm must randomly choose a solution such that all are equally likely to be selected (except the current one). How can this be accomplished in Example 12.13? The constraint that  $x_1 + x_2 + x_3 = 50$  means that  $x_1, x_2$  and  $x_3$  cannot be sampled independently. One might be tempted to sample  $x_1$  as a discrete uniform random variable on 0 to 50, then sample  $x_2$  as a discrete uniform on 0 to  $x_1$  and finally set  $x_2 = x_3 = x_4$ . But this method does not make all solutions equally likely, as the following illustration shows: Suppose that  $x_1$  is randomly sampled to be 50. Then the trial solution must be (50, 0, 0); there is only one choice. But if  $x_1 = x_2$ , then both (49, 1, 0) and (49, 0, 1) are possible. Thus,  $x_1 = x_2$  should be more likely than  $x_1 = x_2$  if all solutions with  $x_1 + x_2 + x_3 = x_4$  are to be equally likely.

#### 12.5 SUMMARY

This chapter provided a basic introduction to the comparative evaluation of alternative system designs based on data collected from simulation runs. It was assumed that a fixed set of alternative system designs had been selected for consideration. Comparisons based on confidence intervals and the use of common random numbers were emphasized. A brief introduction to metamodels—whose purpose is to describe the relationship between design variables and the output response—and to optimization via simulation—whose purpose is to select the best from among a large and diverse collection of system designs—was also provided. There are many additional topics of potential interest (beyond the scope of this text) in the realm of statistical analysis techniques relevant to simulation. Some of these topics are

- 1. experimental design models, whose purpose is to discover which factors have a significant impact on the performance of system alternatives;

- 2. output-analysis methods other than the methods of replication and batch means;

- **3.** variance-reduction techniques, which are methods to improve the statistical efficiency of simulation experiments (common random numbers being an important example).

The reader is referred to Banks [1998] and Law and Kelton [2000] for discussions of these topics and of others relevant to simulation.

The most important idea in Chapters 11 and 12 is that simulation output data require a statistical analysis in order to be interpreted correctly. In particular, a statistical analysis can provide a measure of the precision of the results produced by a simulation and can provide techniques for achieving a specified precision.

#### REFERENCES

ANDRADOTTIR, S. [1998], "Simulation Optimization," Chapter 9 in *Handbook of Simulation*, J. Banks, ed., Wiley, New York.

BANKS, J., ed. [1998], Handbook of Simulation, Wiley, New York.

BECHHOFER, R. E., T. J. SANTNER, AND D. GOLDSMAN [1995], Design and Analysis for Statistical Selection, Screening and Multiple Comparisons, Wiley, New York.

BOESEL, J., B. L. NELSON, AND N. ISHII [2003], "A Framework for Simulation-Optimization Software," *IIE Transactions*, Vol. 35, pp. 221–229.

BOX, G. E. P., AND N. R. DRAPER [1987], Empirical Model-Building and Response Surfaces, Wiley, New York.

FU, M. C. [2002], "Optimization for Simulation: Theory vs. Practice," *INFORMS Journal on Computing*, Vol. 14, pp. 192–215.

GLOVER, F. [1989]. "Tabu Search—Part I." ORSA Journal on Computing, Vol. 1, pp. 190-206.

GOLDSMAN, D., AND B. L. NELSON [1998], "Comparing Systems via Simulation," Chapter 8 in *Handbook of Simulation*, J. Banks, ed., Wiley, New York.

HINES, W. W., D. C. MONTGOMERY, D. M. GOLDSMAN, AND C. M. BORROR [2002], *Probability and Statistics in Engineering*, 4th ed., Wiley, New York.

HOCHBERG Y., AND A. C. TAMHANE [1987], Multiple Comparison Procedures, Wiley, New York

HSU, J. C. [1996], Multiple Comparisons: Theory and Methods. Chapman & Hall, New York.

KLEIJNEN, J. P. C. [1975]. Statistical Techniques in Simulation, Parts 1 and II, Dekker, New York.

KLEIJNEN, J. P. C. [1987], Statistical Tools for Simulation Practitioners, Dekker, New York.

KLEIJNEN, J. P. C. [1988], "Analyzing Simulation Experiments with Common Random Numbers," *Management Science*, Vol. 34, pp. 65–74.

KLEIJNEN, J. P. C. [1998], "Experimental Design for Sensitivity Analysis, Optimization, and Validation of Simulation Models," Chapter 6 in *Handbook of Simulation*, J. Banks, ed., Wiley, New York.

LAW, A. M., AND W. D. KELTON [2000]. Simulation Modeling and Analysis, 3d ed., McGraw-Hill, New York.

MONTGOMERY, D. C. [2000], Design and Analysis of Experiments, 5th ed., Wiley, New York,

NELSON, B. L., AND F. J. MATEJCIK [1995], "Using Common Random Numbers for Indifference-Zone Selection and Multiple Comparisons in Simulation." *Management Science*, Vol. 41, pp. 1935–1945.

NELSON, B. L., J. SWANN, D. GOLDSMAN, AND W.-M. T. SONG [2001], "Simple Procedures for Selecting the Best System when the Number of Alternatives is Large," *Operations Research*, Vol. 49, pp. 950–963.

NELSON, B. L. [1987], "Some Properties of Simulation Interval Estimators Under Dependence Induction," *Operations Research Letters*, Vol. 6, pp. 169–176.

NELSON, B. L. [1992], "Designing Efficient Simulation Experiments," 1992 Winter Simulation Conference Proceedings, pp. 126–132.

WRIGHT, R. D., AND T. E. RAMSAY, JR. [1979], "On the Effectiveness of Common Random Numbers," *Management Science*, Vol. 25, pp. 649–656.

#### **EXERCISES**

1. Reconsider the dump-truck problem of Example 3.5, which was also analyzed in Example 12.2. As business expands, the company buys new trucks, making the total number of trucks now equal to 16. The company desires to have a sufficient number of loaders and scales so that the average number of trucks waiting at the loader queue plus the average number at the weigh queue is no more than three. Investigate the following combinations of number of loaders and number of scales:

| Number of | Number of Loader: |   |   |  |

|-----------|-------------------|---|---|--|

| Scales    | 2                 | 3 | 4 |  |

| 1         | _                 |   | _ |  |

| 2         | _                 | _ |   |  |

The loaders being considered are the "slow" loaders in Example 12.2. Loading time, weighing time, and travel time for each truck are as previously defined in Example 12.2. Use common random numbers to the greatest extent possible when comparing alternative systems designs. The goal is to find the smallest number of loaders and scales to meet the company's objective of an average total queue length of no more than three trucks. In your solution, take into account the initialization conditions, run length, and number of replications needed to achieve a reasonable likelihood of valid conclusions.

2. In Exercise 11.5, consider the following alternative (M, L) policies:

Investigate the relative costs of these policies, using suitable modifications of the simulation model developed in Exercise 11.5. Compare the four system designs on the basis of long-run mean monthly cost. First make four replications of each (M, L) policy, using common random numbers to the greatest

|     |      |     | I                |            |

|-----|------|-----|------------------|------------|

|     |      |     | <i>Low</i><br>30 | High<br>40 |

| M   | Low  | 50  | (50, 30)         | (50, 40)   |

| IVI | High | 100 | (100, 30)        | (100, 40)  |

extent possible. Each replication should have a 12-month initialization phase followed by a 100-month data-collection phase. Compute confidence intervals having an overall confidence level of 90% for mean monthly cost for each policy. Then estimate the additional replications needed to achieve confidence intervals that do not overlap. Draw conclusions as to which is the best policy.

- 3. Reconsider Exercise 11.6. Compare the four inventory policies studied in Exercise 2, taking the cost of rush orders into account when computing monthly cost.

- **4.** In Exercise 11.8, investigate the effect of the order quantity on long-run mean daily cost. Each order arrives on a pallet on a delivery truck, so the permissible order quantities, Q, are multiples of 10 (i.e., Q may equal 10, or 20, or 30, ...). In Exercise 11.8, the policy Q = 20 was investigated.

- (a) First, investigate the two policies Q = 10 and Q = 50. Use the run lengths, and so on, suggested in Exercise 11.8. On the basis of these runs, decide whether the optimal Q, say  $Q^*$ , is between 10 and 50 or is greater than 50. (The cost curve as a function of Q should have what kind of shape?)

- (b) Using the results in part (a), suggest two additional values for Q and simulate the two policies. Draw conclusions. Include an analysis of the strength of your conclusions.

- **5.** In Exercise 11.10, find the number of cards Q that the card shop owner should purchase to maximize the profit with an error of approximately \$5.00. Use the following expression to generate Q value

$$Q = 300 \pm 100$$

For each run, generate a uniform random variate to get the Q value and for that Q value compute profit.

- 6. In Exercise 11.10, investigate the effect of target level M and review period N on mean monthly cost. Consider two target levels, M, determined by  $\pm 10$  from the target level used in Exercise 11.10, and consider review periods N of 1 month and 3 months. Which (N, M) pair is best, according to these simulations?